Функциональное описание цифровых устройств

При составлении моделей сложных цифровых компонентов удобно применять следующие примитивы:

Logic Expression – составление логических выражений (примитив LOGICEXP);

Pin-to-Pin Delay – задание задержек распространения сигналов (примитив PINDLY);

Constraint Cheker – правила проверки временных соотношений, таких, как минимальное время установки/сброса, минимальная длительность импульсов и т. п. (примитив CONSTRAINT). При нарушении этих ограничений в процессе моделирования выдаются предупреждающие соотношения (в PSpice 4 в этих целях использовались два отдельных примитива WDTHCK и SUHDCK).

6.5.1. Логические выражения

Примитив LOGICEXP задается по формату

Uxxx LOGICEXP (<количество входов>,<количество выходов>)

+ <+узел источника питания> <–узел источника питания>

+ <входной узел 1> . . . <входной узел n>

+ <выходной узел 1> . . . <выходной узел n>

+ <имя модели динамики> <имя модели вход/выход>

+ [IO_LEVEL=<уровень модели интерфейса>]

+ [MNTYMXDLY=<выбор значения задержки>]

+ LOGIC:

+ <логическое назначение>*

Логическое назначение записывается двояко:

<номер выходного узла> = {<логическое выражение >}

<промежуточная переменная> = {<логическое выражение >}

Каждый упомянутый в спецификации выходной узел должен иметь одно логическое выражение. Назначенные один раз промежуточные переменные могут использоваться в последующих логических выражениях. Промежуточным переменным присваиваются имена по тем же правилам, что именам узлов.

Логические выражения заключаются в фигурные скобки { }. Они записываются на одной или более строках, строки продолжения имеют символ “+” в первой позиции. Приведем перечень логических операторов в порядке их старшинства:

~ – логическое отрицание;

& – логическое И;

^ – логическое исключающее ИЛИ;

| – логическое ИЛИ.

В качестве операндов могут быть:

– входные узлы;

– предварительно определенные временные переменные;

– предварительно определенные выходные узлы;

– логические константы “0”, “1”, “X”, “R”, “F”.

При записи выражений можно применять круглые скобки для группирования операндов. Все эти логические выражения могут использоваться также и в программе Probe.

Модель динамики примитива LOGICEXP имеет такой же формат, как стандартные вентили:

.MODEL <имя модели> UGATE [(параметры)]

Логические выражения вычисляются в процессе моделирования в порядке их следования. Задержка появления сигналов на выходных узлах определяется в модели динамики. Внутренние обратные связи в логических выражениях не допускаются, однако внешние обратные связи по-прежнему возможны.

Приведем пример описания логики функционирования арифметико-логического устройства 74181. Временные задержки будут заданы ниже с помощью примитивов PINDLY и CONSTRAINT:

U74181 LOGICEXP( 14, 8) DPWR DGND

+ A0BAR A1BAR A2BAR A3BAR B0BAR B1BAR B2BAR

+ B3BAR S0 S1 S2 S3 M CN LF0BAR LF1BAR LF3BAR

+ LAEQUALB LBAR LGBAR LCN+4

+ D0_GATE IO_STD

+

+ LOGIC:

*

*Промежуточные переменные

*

+ I31 = { ~((B3BAR & S3 & A3BAR) | (A3BAR & S2 & ~B3BAR)) }

+ I32 = { ~((~B3BAR & S1) | (S0 & B3BAR) | A3BAR) }

+

+ I21 = { ~((B2BAR & S3 & A2BAR) | (A2BAR & S2 & ~B2BAR)) }

+ I22 = { ~((~B2BAR & S1) | (S0 & B2BAR) | A2BAR) }

+

+ I11 = { ~((B1BAR & S3 & A1BAR) | (A1BAR & S2 & ~B1BAR)) }

+ I12 = { ~((~B1BAR & S1) | (S0 & B1BAR) | A1BAR) }

+

+ I01 = { ~((B0BAR & S3 & A0BAR) | (A0BAR & S2 & ~B0BAR)) }

+ I02 = { ~((~B0BAR & S1) | (S0 & B0BAR) | A0BAR) }

+

+ MBAR = {~M}

+ P = { I31 & I21 & I11 & I01 }

*

* Выходные переменные

*

+ LF3BAR = { (I31 & ~I32) ^

+ ~( (I21 & I11 & I01 & Cn & MBAR) | (I21 & I11 & I02 & MBAR ) |

+ ( I21 & I12 & MBAR) | (I22 & MBAR) ) }

+

+ LF2BAR = { (I21 & ~I22) ^

+ ~( (I11 & I01 & Cn & MBAR) | (I11 & I02 & MBAR ) | ( I12 & MBAR) | )}

+

+ LF1BAR = { (I11 & ~I12) ^~( (Cn & I01 & MBAR) | (I02 & MBAR) ) }

+

+ LF0BAR = { I01 & ~I02) ^~(MBAR & Cn) }

+

+ LGBAR = { ~( I32 | (I31 & I22) | (I31 & I21 & I12) | (I31 & I22 & I11 & I02) ) }

+

+ LCN+4 = { ~LGBAR | (P & Cn) }

+ LPBAR = { ~P }

+ LAEQUALB = { LF3BAR & LF2BAR & LF1BAR & LF0BAR }

6.5.2. Задание задержек распространения

Примитив PINDLY позволяет назначить задержки распространения сигналов сложным устройствам. Один единственный примитив PINDLY позволяет моделировать временные соотношения и выходные характеристики целой интегральной схемы, имеющей в своем составе, в частности, тристабильные вентили. Кроме того, в описание примитива PINDLY допускается включить спецификации контроля длительностей импульсов SETUP, HOLD, WIDTH, FREQ и GENERAL, которые используются в примитиве CONSTRAINT (см. ниже).

Примитив PINDLY задается по формату

Uxxx PINDLY (<количество путей>,

+ <количество входов разрешения> <количество дополнит. узлов>)

+ <+узел источника питания> <–узел источника питания>

+ <входной узел 1> . . . <входной узел n>

+ [<узел разрешения 1> . . . < узел разрешения n>]

+ [<внутренний узел 1> . . . < внутренний узел n>]

+ <выходной узел 1> . . . <выходной узел n>

+ <имя модели вход/выход>

+ [ IO_LEVEL=<уровень модели интерфейса>]

+ [ MNTYMXDLY=<выбор значения задержки>]

+ [ BOOLEAN:

+ <булевское назначение>*]

+ PINDLY:

+ <назначение задержек>*

+ [TRISTATE:

+ ENABLE LO | HI <узел разрешения>

+ <назначение задержек>*]

+ [ SETUP_HOLD: <спецификация времен установки/удержания>]

+ [ WIDTH: <спецификация ширины импульса>]

+ [ FREQ: <спецификация частоты повторения>]

+ [ GENERAL: <общая спецификация>]

Здесь приняты следующие обозначения:

<количество путей> – количество путей распространения сигналов от входных к выходным узлам; при этом количество входов путей должно быть равно количеству выходов. С каждым путем вход–выход ассоциируется задержка, вычисляемая по определенным правилам;

<количество входов разрешения> – спецификация тристабильных узлов, имеющихся в примитиве (может быть равным нулю). Тристабильные узлы используются в секциях TRISTATE;

<количество внутренних узлов> – внутренние узлы используются в выражениях, определяющих задержки, но они не входят в пути вход–выход (может быть равным нулю).

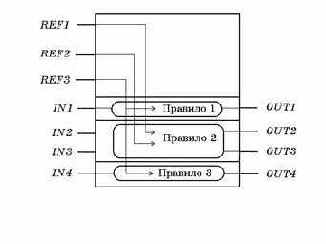

Проиллюстрируем взаимосвязь различных узлов на примере следующего примитива (рис. 6.17):

U1 PINDLY(4, 0, 3) $G_DPWR $G_DGND

+ IN1 IN2 IN3 IN4

+ REF1 REF2 REF3

+ OUT1 OUT2 OUT3 OUT4

+ IO_MODEL D0_GATE

+ PINDLY:

+ . . . .

Рис. 6.17. Правила назначения задержек |

Секция BOOLEAN. С помощью <булевского назначения> определяются промежуточные переменные, которые могут быть использованы в <определении задержки>. Секция BOOLEAN может быть включена на любой строке в описании примитива PINDLY. Выражение <булевское назначение> имеет вид

<булевская переменная> = { <булевское выражение> }

Имя <булевская переменная> составляется по тем же правилам, что имя узла.

Выражение <булевское выражение> принимает значение TRUE (логическая “1”) или FALSE (логический “0”). Подобно всем остальным выражением оно должно быть заключено в фигурные скобки { }. Перечислим булевские операторы в порядке убывания их старшинства:

|

Оператор |

Название |

|

~ |

Логическое отрицание |

|

== |

Равно |

|

!= |

Не равно |

|

& |

Логическое И |

|

^ |

Логическое исключающее ИЛИ |

|

| |

Логическое ИЛИ |

– предварительно определенные <булевские переменные>;

– функции дополнительных узлов (см. ниже);

– функции изменений (см. ниже);

– <булевские константы> TRUE и FALSE.

Дополнительно операторы “==“ и “!=“ могут быть применены к логическим значениям <входные узлы> и <логические константы>. Это позволяет проанализировать логические состояния узлов, например, выражение CLEAR==1 принимает значение TRUE, если узел CLEAR имеет значение логической “1”, и FALSE – в противоположном случае.

Управляющие функции используются для определения изменений состояний <внутренних узлов> или <выходных узлов>. Все управляющие функции принимают логические значения и поэтому могут входить в состав <булевских выражений>. Приведем список этих функций и их аргументов:

CHANGED (<узел>,<интервал времени>)

CHANGED_LH (<узел>,<интервал времени>)

CHANGED_HL (<узел>,<интервал времени>)

Функция CHANGED принимает значение TRUE, если указанный <узел> изменял свое состояние из 0 в 1 на указанном <интервале времени>, предшествующем текущему моменту времени, в противном случае – FALSE.

Аналогично функция CHANGED_LH принимает значение TRUE, если указанный <узел> изменял свое состояние на указанном <интервале времени>, предшествующем текущему моменту времени, в противном случае – FALSE. Отметим, что CHANGED_LH контролирует только самое последнее изменение.

Наконец, функция CHANGED_HL принимает аналогичные значения, контролируя переходы из “1” в “0”.

Если <интервал времени> задать равным нулю, то рассматриваемые функции примут значение TRUE, если в данный момент времени состояние узла изменяется. Это дает возможность разбивать модель цифровых компонентов на две части: первая моделирует логику функционирования с нулевыми задержками, а вторая учитывает реальные задержки.

Функции изменений предназначены для контроля за изменением состояний <выходных узлов>, для которых вычисляются <выражения для задержек>. Подобно дополнительным функциям они принимают значения логического “0” или “1”. Однако в отличие от них они не имеют аргументов и просто фиксируют изменение состояний выходных узлов в текущий момент времени. Они имеют вид

TRN_pn

Здесь p – значение предыдущего состояния, а n – нового состояния. Логические значения состояний обозначаются символами L (низкий уровень), H (высокий уровень) Z (большое выходное сопротивление) и $ (любой уровень). Так, например, функция TRN_H$ контролирует переход из состояния логическая “1” в любое другое состояние.

Замечание. Функции TRN_pZ и TRN_Zn

принимают значение TRUE, только если они используются в секции TRISTATE, описываемой ниже. Хотя выходные узлы устройств с открытым коллектором переходят в состояние высокого импеданса Z (вместо H), в справочниках обычно приводятся значения задержек TPLH и TPHL. Поэтому в математических моделях устройств с открытым коллектором необходимо использовать функции TRN_LH и TRNHL, а в тристабильных устройствах – TRN_LZ, TRN_HZ, TRN_ZL и TRN_ZH.

Секция PINDLY. Ключевое слово PINDLY отмечает начало секции, содержащей одно или несколько <назначений задержек>, которые имеют формат

<выходной узел>* = { <выражение для задержек> }

Каждый <выходной узел>, перечисленный в спецификации примитива, должен иметь одно выражение для определения задержек. Причем несколько выходных узлов могут иметь общее <выражение для задержек> (на рис. 6.17 <выражение для задержек> обозначено как “Правило”), тогда в левой части назначения задержек помещается список их имен, разделяемых пробелами или запятыми.

<Выражение для задержек> заключается в фигурные скобки и может располагаться на нескольких строках. Это выражение имеет три значения задержек: минимальное, типичное и максимальное. В простейшем случае <выражение для задержек> представляет собой <значение задержек> вида

DELAY(<min>, <typ>, <max>),

где <min>, <typ>, <max> – константы с плавающей запятой или выражения (в том числе и параметры), в секундах.

Для спецификации неизвестной величины используется –1. Например, DELAY(20ns, –1,35ns) задает минимальную задержку 20 нс, устанавливаемую программой по умолчанию типичную задержку и максимальную задержку 35 нс.

В более сложных <выражениях для задержек> используются функции CASE вида

CASE

(

<булевское выражение>,< выражение для задержек>, ;Правило 1

<булевское выражение>,< выражение для задержек>, ;Правило 2

. . .

<выражение для задержек> ;Задержки по умолчанию

)

Аргументами функции CASE являются пары <булевское выражение>, <выражение для задержек>, замыкаемые финальным <выражением для задержек>, определяющим значение задержки по умолчанию. При вычислении функции CASE вычисляются <булевские выражения> в порядке их следования до тех пор, пока не будет получен результат TRUE. После этого задержкам присваиваются значения из соответствующего выражения. Если ни одно из выражений не имеет значения TRUE, задержкам присваиваются значения из последнего выражения.

Приведем пример:

. . .

+ BOLEAN:

+ CLOCK = { CHANGED_LH( CLK, 0 ) }

+ PINDLY:

+ QA QB QC QD = {

+ CASE (

+ CLOCK & TRN_LH, DELAY(–1, 13ns, 24ns),

+ CLOCK & TRN_HL, DELAY(–1, 18ns, 27ns),

+ CHANGED_HL(CLBAR,0), DELAY(–1,20ns,28ns),

+ DELAY(–1, 20ns, 28ns) ; По умолчанию

+ )

+ }

В этом примере рассматривается четырехразрядный счетчик. Вводится булевская переменная CLOCK, которая принимает значение TRUE, когда дополнительный узел CLK изменяет свое состояние из “0” в “1” в текущий момент времени. Четыре выхода QA, ..., QD имеют одно и то же правило определения задержек. Функция CASE позволяет назначить разные задержки в процессе счета или обнуления. Первые два правила определяют задержки в процессе счета (CLK изменяется из состояния “0” в “1”). Первое правило применяется при изменении состояний выходов из “0” в “1”, второе – из “1” в “0”. Третье правило непосредственно определяет задержки, когда изменяется состояние узла CLRBAR.

Секция TRISTATE содержит одно или более <назначений задержек>. В отличие от секции PINDLY здесь состояния выходных узлов контролируются с помощью специальных узлов разрешения (enable). Непосредствено после ключевого слова TRISTATE указываются имена узлов разрешения и их полярность с помощью ключевого слова ENABLE по формату

ENABLE HI <узел разрешения> ; Разрешение в состоянии “1”

ENABLE LO <узел разрешения> ; Разрешение в состоянии “0”

Указанный <узел разрешения> управляет назначениям всех выходных узлов текущей секции. Отметим, что <выражения для задержек> в секции TRISTATE может содержать функции изменений, связанных с состоянием высокого импеданса, например TRN_ZL и TRN_HZ.

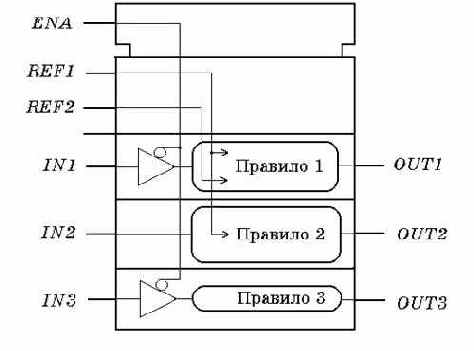

Приведем пример, демонстрирующий применение узлов разрешения для контролирования более чем одного выхода. Здесь также показано, что некоторые выходы могут быть обычными (PINDLY), а другие тристабильными (значения задержек опущены):

U1 PINDLY(3, 1, 2) $G_DPWR $G_DGND

+ IN1 IN2 IN3

+ ENA

+ REF1 REF2

+ OUT1 OUT2 OUT3

+ IO_MODEL

+ TRISTATE:

+ ENABLE LO = ENA

+ OUT1 = {

+ CASE (

+ CHANGED (REF1, 0) & TRN_LH, DELAY(. . .),

+ CHANGED (REF2, 0) DELAY(. . .),

+ TRN_ZL, DELAY(. . .),

+ . . .

+ )

+ }

+ OUT3 = {

+ CASE (

+ TRN_LZ, DELAY(. . .),

+ TRN_HZ, DELAY(. . .),

+ . . .

+ )

+ }

+ PINDLY:

+ OUT2 = {

+ CASE (

+ CHANGED (REF1, 0), DELAY(. . .),

+ . . .

+ )

+ }

Рис. 6.18. Управление задержками с помощью узлов разрешения |

Функционирование примитива PINDLY. Состояния выходных узлов примитива PINDLY изменяются при изменении состояний любого входного узла или узла разрешения. Каждому входному узлу соответствует выходной узел. Сначала определяются состояния внутренних переменных в секции BOOLEAN, затем вычисляются <выражения для задержек> в секциях PINDLY или TRISTATE. После этого изменившееся состояние входного узла присваивается соответствующему ему выходному узлу с задержкой.

Приведем пример реального счетчика 74LS160A:

ULS160ADLY PINDLY (5,0,10) DPWR DGND

+ RCO QA QB QC QD ; Входы

+ CLK LOADBAR ENT CLRBAR ; Внутренние узлы

+ RCO_O QA_O QB_O QC_O QD_O ; Выходы

+ IO_LS MNTYMXDLY = {MNTYMXDLY} IO_LEVEL = {IO_LEVEL}

+

+ BOOLEAN:

+ CLOCK = { CHANGED_LH (CLK, 0) }

+ CNTENT = { CHANGED (ENT, 0) }

+

+ PINDLY:

+ QA_O QB_O QC_O QD_O = {

+ CASE (

+ CLOCK & TRN_LH, DELAY( -1, 13NS, 24NS),

+ CLOCK & TRN_HL, DELAY( -1, 18NS, 27NS),

+ CHANGED_HL ( CLRBAR, 0), DELAY( -1, 20NS, 28NS),

+ DELAY( -1, 20NS, 28NS) ; По умолчанию

+ )

+ }

+ RCO_O = {

+ CASE (

+ CNTENT, DELAY( -1, 9NS, 14NS),

+ CLOCK & TRN_LH, DELAY( -1, 20NS, 35NS),

+ CLOCK & TRN_HL, DELAY( -1, 18NS, 35NS),

+ DELAY( -1, 20NS, 35NS) ; По умолчанию

+ )

+ }

6.5.3. Контроль временных соотношений

Примитив CONSTRAINT выполняет проверку соблюдения временных соотношений в процессе моделирования. Контролируется минимальное время установки/сброса, минимальная длительность импульсов, частота переключений и предусмотрен общий механизм проверки условий, формулируемых пользователем. Примитив CONSTRAINT только сообщает о нарушении временных сообщений и не изменяет логические состояния узлов и задержки. Он задается по формату

Uxxx CONSTRAINT ( <количество входов> )

+ <+узел источника питания> <–узел источника питания>

+ <входной узел 1> . . . <входной узел n>

+ <имя модели вход/выход>

+ [ IO_LEVEL=<уровень модели интерфейса>]

+ [ BOOLEAN: <булевское назначение> * ] ...

+ [ SETUP_HOLD: <спецификация времен установки/удержания>] ...

+ [ WIDTH: <спецификация ширины импульса> ] ...

+ [ FREQ: <спецификация частоты повторения> ] ...

+ [ GENERAL: <общая спецификация> ] ...

Секция BOOLEAN содержит одно или несколько <булевских назначений> вида

<булевская переменная> = { <булевское выражение> }

Секции BOOLEAN могут включаться в любом порядке при описании примитива CONSTRAINT. Синтаксис <булевских выражений> такой же, что и в примитиве PINDLY, за исключением того, что не могут быть использованы функции изменений.

Секция SETUP_HOLD выполняет проверку времен установки/сброса, она имеет формат

+ SETUP_HOLD:

+ CLOCK <определение типа перехода>=<входной узел>

+ DATA (<кол-во входов данных>)=<входной узел j>...< входной узел k>

+ [ SETUPTIME=<значение интервала времени>]

+ [ HOLDTIME=< значение интервала времени

> ]

+ [ RELEASETIME = < значение интервала времени > ]

+ [ WHEN { <булевское выражение> } ]

+ [ MESSAGE=“<текст дополнительного сообщения>“]

+ [ ERRORLIMIT=<значение> ]

+ [ AFFECTS_ALL | AFFECTS_NONE |

+ AFFECTS (#OUTPUTS)=<список выходных узлов>]

CLOCK задает узел, относительно которого выполняется измерение длительности времен установки/удержания/отпускания. Параметр <определения типа перехода> принимает значения LH или HL, он указывает, от какого фронта импульса (0

DATA определяет перечень узлов, для которых выполняется измерение времен установки/удержания.

SETUPTIME определяет минимальное время, в течение которого все узлы, перечисленные в разделе DATA, должны находиться в неизменном состоянии до момента начала отсчета времен установки/удержания. <

значение интервала времени > должно быть неотрицательной константой или выражением (в секундах). Некоторые устройства имеют различные требования к времени установки в зависимости от состояния входных данных (“0” или “1”) в момент начала отсчета. В таком случае вместо SETUPTIME применяется одна из форм

SETUPTIME_LO=<значение интервала времени>]

SETUPTIME_HI=<значение интервала времени>]

HOLDTIME определяет минимальное время, в течение которого все узлы, перечисленные в разделе DATA, должны находиться в неизменном состоянии после момента начала отсчета времен установки/удержания. <

значение интервала времени > должно быть неотрицательной константой или выражением (в секундах). Некоторые устройства имеют различные требования к времени установки в зависимости от состояния входных данных (“0” или “1”) в момент начала отсчета. В таком случае вместо HOLDTIME применяется одна из форм

HOLDTIME_LO=<значение интервала времени>]

HOLDTIME_HI=<значение интервала времени>]

RELEASETIME содержит спецификацию времени восстановления – минимального интервала времени стабильного состояния, предшествующего переключению. Если время восстановления зависит от направления переключения входных данных, то вместо RELEASETIME применяется одна из форм

RELEASETIME _LH=<значение интервала времени>]

RELEASETIME _HL=<значение интервала времени>]

Разница между проверкой времени восстановления и установления состоит в том, что при контроле времени восстановления не разрешается одновременное изменение CLOCK/DATA. Поэтому, если даже время удержания HOLDTIME явно не задано, оно считается больше нуля. Это свойство позволяет задать значения времени восстановления непосредственно в тексте описания модели. По этой причине время восстановления обычно задается отдельно, независимо от спецификаций SETUPTIME или HOLDTIME.

Проверка времен установления/удержания/восстановления начинается после того, как наступило заданное изменение состояния узла CLOCK (LH или HL). В этот момент времени вычисляется логическое выражение WHEN. Если оно принимает значение TRUE, то выполняются все проверки, имеющие ненулевые значения интервалов времени.

WIDTH содержит спецификацию минимальной длительности импульса следующего вида:

+ WIDTH

+ NODE=<входной узел>

+ [ MIN_HI=< значение интервала времени

> ]

+ [ MIN_LO=< значение интервала времени

> ]

+ [ WHEN { <булевское выражение> } ]

+ [ MESSAGE=“<текст дополнительного сообщения>“]

+ [ ERRORLIMIT=<значение> ]

+ [ AFFECTS_ALL | AFFECTS_NONE |

+ AFFECTS (#OUTPUTS)=<список выходных узлов>]

Переменная NODE указывает входной узел, для которого проводится контроль длительности импульса. MIN_HI задает минимальное время, в течение которого входной узел должен находиться в состоянии “1”, а MIN_LO – в состоянии “0”. Если значение MIN_HI не указано, то оно считается равным нулю, что означает отсутствие ограничений на минимальную длительность импульсов.

FREQ содержит спецификацию допустимой частоты переключений:

+ FREQ

+ NODE=<входной узел>

+ [ MINFREQ=< значение частоты

> ]

+ [ MAXFREQ=< значение частоты

> ]

+ [ WHEN { <булевское выражение> } ]

+ [ MESSAGE=“<текст дополнительного сообщения>“]

+ [ ERRORLIMIT=<значение> ]

+ [ AFFECTS_ALL | AFFECTS_NONE |

+ AFFECTS (#OUTPUTS)=<список выходных узлов>]

Переменная NODE указывает входной узел, для которого проводится контроль частоты переключений. MINFREQ задает минимальное частоту переключений, а MAXFREQ – максимальную.

При моделировании выводятся предупреждающие сообщения, когда период переключений больше/меньше значений 1/<значение частоты>.

GENERAL содержит спецификацию проверок, формулируемых пользователем

+ GENERAL

+ WHEN { <булевское выражение> }

+ MESSAGE=“<текст дополнительного сообщения>“

+ [ ERRORLIMIT=<значение> ]

+ [ AFFECTS_ALL | AFFECTS_NONE |

+ AFFECTS (#OUTPUTS)=<список выходных узлов>]

Переменная WHEN задает правило контроля в виде булевского выражения. Текст сообщения об ошибки задается с помощью переменной MESSAGE.

Общие замечания. Спецификации контроля SETUP_HOLD, WIDTH, FREQ, GENERAL могут располагаться в тексте примитива CONSTRAINT в любом порядке. Более того, спецификация каждого типа может встречаться несколько раз. Каждая спецификация может содержать предложение WHEN, тогда проверка выполняется, если указанное в нем <булевское выражение> истинно. Проверка GENERAL содержит предложение WHEN всегда. Все проверки содержат встроенные соообщения об ошибках. Дополнительные сообщения можно вывести с помощью спецификации MESSAGE.

Все проверки имеют необязательный параметр ERRORLIMIT, определяющий максимальное количество ошибок. По умолчанию оно принимается равным значению глобальной переменной DIGERRDEFAULT (см. директиву .OPTIONS), обычно 20. Значение этого параметра, равное нулю, интерпретируется как бесконечное значение. В случае, когда количество ошибок данного типа превышает максимальное, сообщения об ошибках больше не выводятся на экран программы PSpice и в выходной файл .out.

Если в процессе моделирования общее количество ошибок превышает значение глобального параметра DIGERRLIMIT (см. директиву .OPTIONS), моделирование прекращается. По умолчанию значение DIGERRLIMIT устанавливается равным бесконечности.

Приведем пример примитива CONSTRAINT из текста модели счетчика 74LS160A, демонстрирующий возможности осуществления всех проверок с помощью одного примитива:

ULS160ACON CONSTRAINT (10) DRR DGND

+ CLK ENP ENT CLBAR LOADBAR A B C D EN

+ IO_LS

+ FREQ:

+ NODE = CLK

+ MAXFREQ = 25MEG

+ WIDTH:

+ NODE = CLK

+ MIN_LO = 25NS

+ MIN_HI = 25NS

+ WIDTH:

+ NODE = CLRBAR

+ MIN_LO = 20NS

+ SETUP_HOLD:

+ DATA(1) = LOADBAR

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ HOLDTIME = 3NS

+ WHEN = { CLRBAR!='0 }

+ SETUP_HOLD:

+ DATA(2) = ENP ENT

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ HOLDTIME = 3NS

+ WHEN = { CLRBAR!= '0 & (LOADBAR!= '0 ^ CHANGED (LOADBAR,0))

+ & CHANGED(EN,20NS) }

+ SETUP_HOLD:

+ DATA(4) = A B C D

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ HOLDTIME = 3NS

+ WHEN = { CLRBAR!= '0 & (LOADBAR!='1 ^ CHANGED(LOADBAR,0)) }

+ SETUP_HOLD:

+ DATA(1) = CLRBAR

+ CLOCK LH = CLK

+ RELEASETIME_LH = 25NS